S5L8701 analysis: Difference between revisions

No edit summary |

|||

| Line 6: | Line 6: | ||

Knowing the location of some JTAG pins could be very helpful. | Knowing the location of some JTAG pins could be very helpful. | ||

There is an OpenOffice Calc document describing possible pinouts [http://f4eru.free.fr/8701 | There is an OpenOffice Calc document describing possible pinouts [http://f4eru.free.fr/8701/ here]. There is also [https://mail.gna.org/public/linux4nano-dev/2009-05/msg00003.html tof's mailing list post]. | ||

== Structure of the packaging == | == Structure of the packaging == | ||

| Line 43: | Line 43: | ||

== Guessed pinout table == | == Guessed pinout table == | ||

the pinout is currently under study. See [http://f4eru.free.fr/8701/ here] | |||

one more broken nano 2G wanted. | |||

Revision as of 13:33, 31 May 2009

Introduction

The samsung S5L8701 is the SOC of the IN2G. This chip is supposed to be close to the 8700 used on some concurrent MP3 players.

We currently know nearly nothing about the differences of both chips, and the further evolutions. There is probably a small unencrypted boot ROM inside, which would be very useful for integrating user SW. Probably containing crypto information. Knowing the location of some JTAG pins could be very helpful.

There is an OpenOffice Calc document describing possible pinouts here. There is also tof's mailing list post.

Structure of the packaging

The chip is a 226-pin TFBGA with a pitch of 0.5mm. This is the structure of a BGA package : BGA package

The chip is glued to a small double side PCB substrate. the electrical current passes through :

-a pad of the chip die -a bonding wire -the top layer of the substrate -a via -the bottom layer -finally, the BGA ball

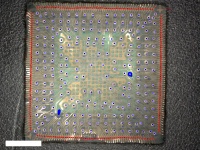

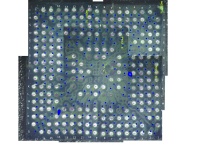

The known datasheet shows die pad numbers that need to be correlated to ball numbers (the specified package has a different ball layout). In order to do this, we make an analysis of the bonding and PCB.

Packaging analysis

Following steps were made :

-desoldering of the IC -removing of the balls and filler glue -X-ray picture -microscope picture of the bottom layer -removing the bottom layer and most of the substrate (by careful manual grinding) -microscope picture of the top layer -superposition of these views, and path finding from the die to the ball

Guessed pinout table

the pinout is currently under study. See here

one more broken nano 2G wanted.