Nano 7G: Difference between revisions

Nano 7G

m move images to components section |

|||

| (7 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

{{DISPLAYTITLE:iPod nano (7th generation)}} | |||

==Components== | ==Components== | ||

[[File:Nano7g_front.jpg|500px|thumb|none|Photo of the circuit board]] | |||

[[File:Nano7g_back.jpg|500px|thumb|none|Close up of the larger chips on the circuit board]] | |||

{| class="wikitable" | {| class="wikitable" | ||

! Label !! Component !! Part !! Markings !! Notes | ! Label !! Component !! Part !! Markings !! Notes | ||

| Line 62: | Line 63: | ||

| 8740 per IMG1. Guessing based on similar package to N6G SoC/CPU. Also has the most diffpairs running to/from it (from delayered PCB). | | 8740 per IMG1. Guessing based on similar package to N6G SoC/CPU. Also has the most diffpairs running to/from it (from delayered PCB). | ||

|} | |} | ||

==Helpful pages== | ==Helpful pages== | ||

| Line 73: | Line 71: | ||

* TODO | * TODO | ||

--> | --> | ||

== Core == | |||

Cortex A5 according to CP15: | |||

<pre> | |||

ID code: 0x410fc050 | |||

Implementer: ARM | |||

Variant: 0x0 | |||

Architecture: See CPUID | |||

Part number: c05, Revision: 0 | |||

</pre> | |||

== Memory Map == | |||

{| class="wikitable" | |||

! Address !! Name | |||

|- | |||

| 0x38C00000 | |||

| AES | |||

|- | |||

| 0x3C500000 | |||

| CLKCON | |||

|- | |||

| 0x3C700000 | |||

| TIMER | |||

|- | |||

| 0x3CC00000 | |||

| UART0 | |||

|- | |||

| 0x3CF00000 | |||

| GPIO | |||

|- | |||

| 0x3D100000 | |||

| CHIPID | |||

|} | |||

== Clock Gates == | |||

There is no big debug table with all clock gates in N7G RetailOS, so the following has been written out by hand: | |||

{| class="wikitable" | |||

! Address !! Bits (clear to power on) !! Meaning !! Source | |||

|- | |||

| 0x3C50006C | |||

| 0x2000 | |||

| 'SPI power' | |||

| WTF DevicePowerManagement.dll | |||

|- | |||

| 0x3C50004C | |||

| 0x4 | |||

| 'SPI power' | |||

| WTF DevicePowerManagement.dll | |||

|- | |||

| 0x3C50004c | |||

| 0x1f800020 | |||

| Timer | |||

| WTF IpodSec.dll | |||

|- | |||

| 0x3C500058 | |||

| 0x60 | |||

| Timer | |||

| WTF IpodSec.dll | |||

|- | |||

| 0x3c50006c | |||

| 0xc0007f | |||

| Timer | |||

| WTF IpodSec.dll | |||

|} | |||

Latest revision as of 04:56, 23 June 2025

Components

| Label | Component | Part | Markings | Notes |

|---|---|---|---|---|

| Red | PMIC | Apple 338S1099 | Guessing based on connectivity to power components around. | |

| Orange | Bluetooth + FM radio | Broadcom BCM2078KUBG | ||

| Yellow | NXP Semiconductors 1609A1 | |||

| Green | 75203 23017 | |||

| Blue | 75292 98820 |

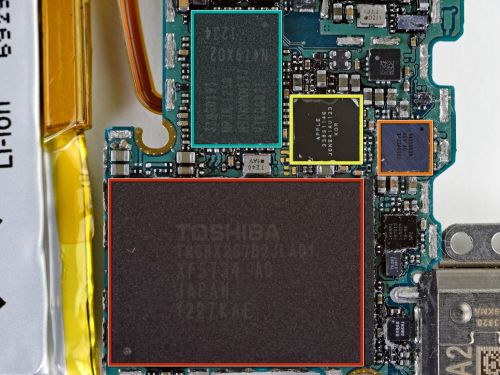

| Label | Component | Part | Markings | Notes |

|---|---|---|---|---|

| Red | NAND flash | Toshiba THGBX2G7D2JLA01 128 Gb (16 GB) | ||

| Orange | Touchscreen controller | Texas Instruments 343S0538 | ||

| Yellow | Apple 338S1146 | |||

| Green | SoC/CPU | S5L8740 | 339S0193 | 8740 per IMG1. Guessing based on similar package to N6G SoC/CPU. Also has the most diffpairs running to/from it (from delayered PCB). |

Helpful pages

Teardowns:

Core

Cortex A5 according to CP15:

ID code: 0x410fc050 Implementer: ARM Variant: 0x0 Architecture: See CPUID Part number: c05, Revision: 0

Memory Map

| Address | Name |

|---|---|

| 0x38C00000 | AES |

| 0x3C500000 | CLKCON |

| 0x3C700000 | TIMER |

| 0x3CC00000 | UART0 |

| 0x3CF00000 | GPIO |

| 0x3D100000 | CHIPID |

Clock Gates

There is no big debug table with all clock gates in N7G RetailOS, so the following has been written out by hand:

| Address | Bits (clear to power on) | Meaning | Source |

|---|---|---|---|

| 0x3C50006C | 0x2000 | 'SPI power' | WTF DevicePowerManagement.dll |

| 0x3C50004C | 0x4 | 'SPI power' | WTF DevicePowerManagement.dll |

| 0x3C50004c | 0x1f800020 | Timer | WTF IpodSec.dll |

| 0x3C500058 | 0x60 | Timer | WTF IpodSec.dll |

| 0x3c50006c | 0xc0007f | Timer | WTF IpodSec.dll |