Difference between revisions of "Nano 5G"

Nano 5G

| Line 9: | Line 9: | ||

| Samsung S5L8730 | | Samsung S5L8730 | ||

| 339S0081 ARM, K4X51323PG-UGC6, EDE168AG 0928, APL0378A00, N1X2XW 0931 | | 339S0081 ARM, K4X51323PG-UGC6, EDE168AG 0928, APL0378A00, N1X2XW 0931 | ||

| − | | Printed backwards on the chip - how sneaky. | + | | Printed backwards on the chip - how sneaky. ARM1176JZF-S core (per CP15 data). |

|- | |- | ||

| | | | ||

| Line 58: | Line 58: | ||

| 0630, CK9Y, 925 | | 0630, CK9Y, 925 | ||

| | | | ||

| + | |} | ||

| + | |||

| + | == CP15 Registers == | ||

| + | |||

| + | Dump of CP15 registers from bootrom context: | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! cX !! cY !! opc2 !! Description !! Value !! Interpretation | ||

| + | |- | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | Main ID | ||

| + | | 410fb764 | ||

| + | | ARM (0x41), Variant 0, Architecture: see CPUID, Part: ARM1176 | ||

| + | |- | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | Cache Type | ||

| + | | 1d152152 | ||

| + | | Write back, format C cache lockdown, Register 7 cache cleaning operations, separate I/D caches; data cache: (no restriction on page allocation, 16KB, 4-way associative, 2 word line length) istrunction cache: (no restrictions on page allocation, 16KB, 4-way, 2 word) | ||

| + | |- | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 2 | ||

| + | | TCM Status | ||

| + | | 00000000 | ||

| + | | No tightly coupled memory. | ||

| + | |- | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 3 | ||

| + | | TLB Type | ||

| + | | 00000800 | ||

| + | | | ||

| + | |- | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | Processor Feature 0 | ||

| + | | 00000111 | ||

| + | | Jazelle, Thumb1, ARM (no Thumb2) | ||

| + | |- | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | Processor Feature 1 | ||

| + | | 00000011 | ||

| + | | Security Extensions Architecture v1, Standard ARMv4 programmer's model. No microcontroller model. | ||

| + | |- | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 2 | ||

| + | | Debug Feature 0 | ||

| + | | 00000033 | ||

| + | | v6.1 Secure Debug, v6.1 Debug. | ||

| + | |- | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 3 | ||

| + | | Auxiliary Feature 0 | ||

| + | | 00000000 | ||

| + | | | ||

| + | |- | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 4 | ||

| + | | Memory Model Feature 0 | ||

| + | | 01130003 | ||

| + | | Standard ARM1176JZF-S. | ||

| + | |- | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 5 | ||

| + | | Memory Model Feature 1 | ||

| + | | 10030302 | ||

| + | | Standard ARM1176JZF-S. | ||

| + | |- | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 6 | ||

| + | | Memory Model Feature 2 | ||

| + | | 01222100 | ||

| + | | Standard ARM1176JZF-S. | ||

| + | |- | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 7 | ||

| + | | Memory Model Feature 3 | ||

| + | | 00000000 | ||

| + | | Standard ARM1176JZF-S. | ||

| + | |- | ||

| + | | 0 | ||

| + | | 2 | ||

| + | | 0 | ||

| + | | Instruction Set Feature Attribute 0 | ||

| + | | 00140011 | ||

| + | | Standard ARM1176JZF-S. | ||

| + | |- | ||

| + | | 0 | ||

| + | | 2 | ||

| + | | 1 | ||

| + | | Instruction Set Feature Attribute 1 | ||

| + | | 12002111 | ||

| + | | Standard ARM1176JZF-S. | ||

| + | |- | ||

| + | | 0 | ||

| + | | 2 | ||

| + | | 2 | ||

| + | | Instruction Set Feature Attribute 2 | ||

| + | | 11231121 | ||

| + | | Standard ARM1176JZF-S. | ||

| + | |- | ||

| + | | 0 | ||

| + | | 2 | ||

| + | | 3 | ||

| + | | Instruction Set Feature Attribute 3 | ||

| + | | 01102131 | ||

| + | | Standard ARM1176JZF-S. | ||

| + | |- | ||

| + | | 0 | ||

| + | | 2 | ||

| + | | 4 | ||

| + | | Instruction Set Feature Attribute 4 | ||

| + | | 00001141 | ||

| + | | Standard ARM1176JZF-S. | ||

| + | |- | ||

| + | | 0 | ||

| + | | 2 | ||

| + | | 5 | ||

| + | | Instruction Set Feature Attribute 5 | ||

| + | | 00000000 | ||

| + | | Standard ARM1176JZF-S. | ||

| + | |- | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | Control | ||

| + | | 00450078 | ||

| + | | No Force AP, no TEX remap, CPSR E set to 0 on exception, no VIC, no extended page tables, allow unaligned data access, no fast interrupts, global enable for instruction/data TCM, loads to PC set the T bit, random cache replacement, exceptions vectors at Vector Base Address Register. I$, D$ disabled by wInd3x, branch prediction disabled, no strict alignment fault checking, no MMU. | ||

| + | |- | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | Auxiliary Control | ||

| + | | 00000007 | ||

| + | | ... | ||

| + | |- | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 2 | ||

| + | | Coprocessor Access Control | ||

| + | | 00000000 | ||

| + | | ... | ||

| + | |- | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | Secure Configuration | ||

| + | | 00000000 | ||

| + | | ... | ||

| + | |- | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | Secure Debug Enable | ||

| + | | 00000000 | ||

| + | | ... | ||

| + | |- | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 2 | ||

| + | | Non-Secure Access Control | ||

| + | | 00000000 | ||

| + | | ... | ||

| + | |- | ||

| + | | 2 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | Translation Table Base 0 | ||

| + | | 00000000 | ||

| + | | ... | ||

| + | |- | ||

| + | | 2 | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | Translation Table Base 1 | ||

| + | | 00000000 | ||

| + | | ... | ||

| + | |- | ||

| + | | 2 | ||

| + | | 0 | ||

| + | | 2 | ||

| + | | Translation Table Base Control | ||

| + | | 00000000 | ||

| + | | ... | ||

| + | |- | ||

| + | | 3 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | Domain Access Control | ||

| + | | 00000000 | ||

| + | | ... | ||

| + | |- | ||

| + | | 7 | ||

| + | | 4 | ||

| + | | 0 | ||

| + | | PCA | ||

| + | | 00000000 | ||

| + | | ... | ||

| + | |- | ||

| + | | 7 | ||

| + | | 10 | ||

| + | | 6 | ||

| + | | Cache Dirty Status | ||

| + | | 00000000 | ||

| + | | ... | ||

| + | |- | ||

| + | | 9 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | Data Cache Lockdown | ||

| + | | fffffff0 | ||

| + | | ... | ||

| + | |- | ||

| + | | 9 | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | Instruction Cache Lockdown | ||

| + | | fffffff0 | ||

| + | | ... | ||

| + | |- | ||

| + | | 9 | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | Data TCM Region | ||

| + | | 00000000 | ||

| + | | ... | ||

| + | |- | ||

| + | | 9 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | Instruction TCM Region | ||

| + | | 00000000 | ||

| + | | ... | ||

| + | |- | ||

| + | | 9 | ||

| + | | 1 | ||

| + | | 2 | ||

| + | | Data TCM Non-secure Control Access | ||

| + | | 00000000 | ||

| + | | ... | ||

| + | |- | ||

| + | | 9 | ||

| + | | 1 | ||

| + | | 3 | ||

| + | | Instruction TCM Non-secure Control Access | ||

| + | | 00000000 | ||

| + | | ... | ||

| + | |- | ||

| + | | 9 | ||

| + | | 2 | ||

| + | | 0 | ||

| + | | TCM Selection | ||

| + | | 00000000 | ||

| + | | ... | ||

| + | |- | ||

| + | | 9 | ||

| + | | 8 | ||

| + | | 0 | ||

| + | | Cache Behavior Override | ||

| + | | 00000000 | ||

| + | | ... | ||

|} | |} | ||

Revision as of 20:40, 14 October 2022

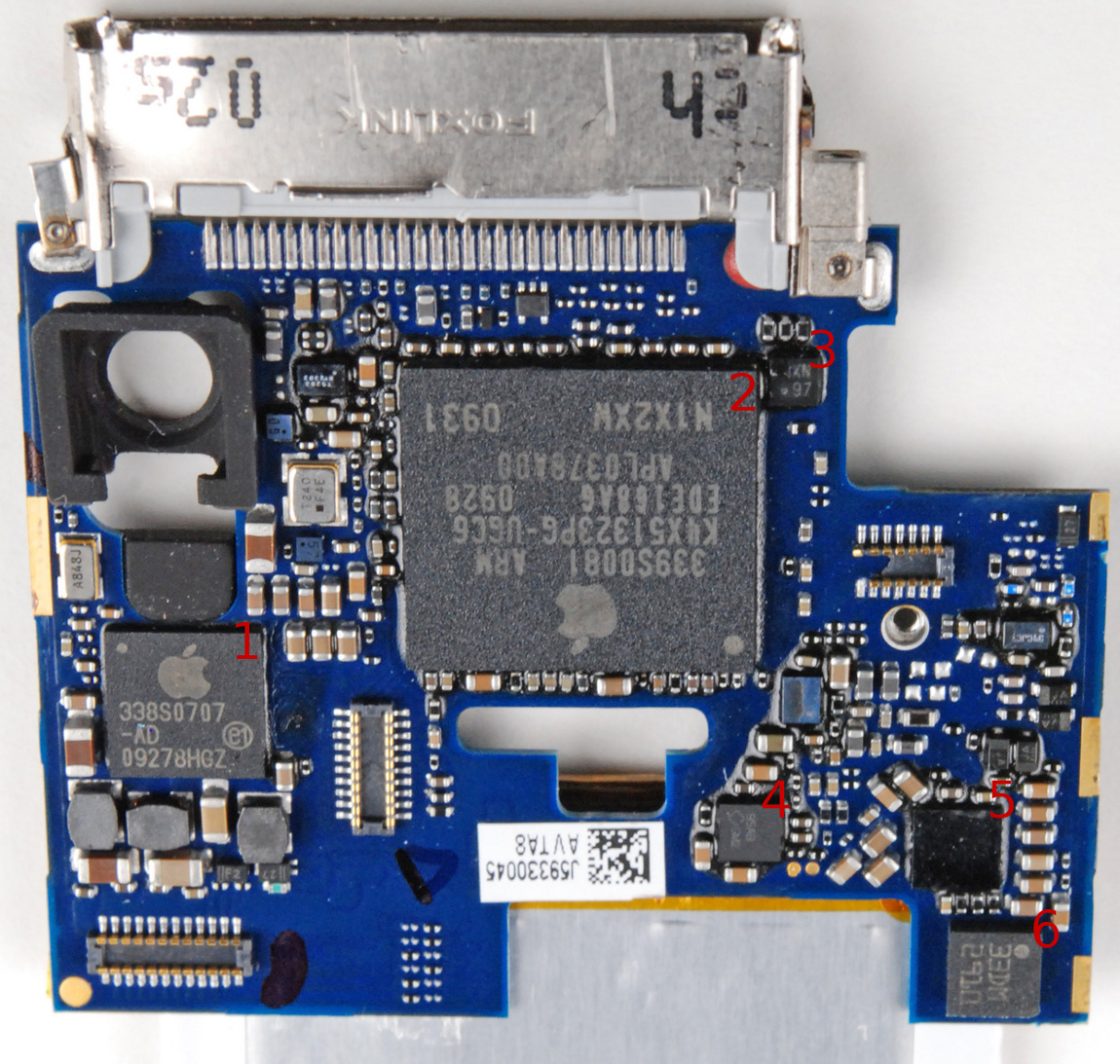

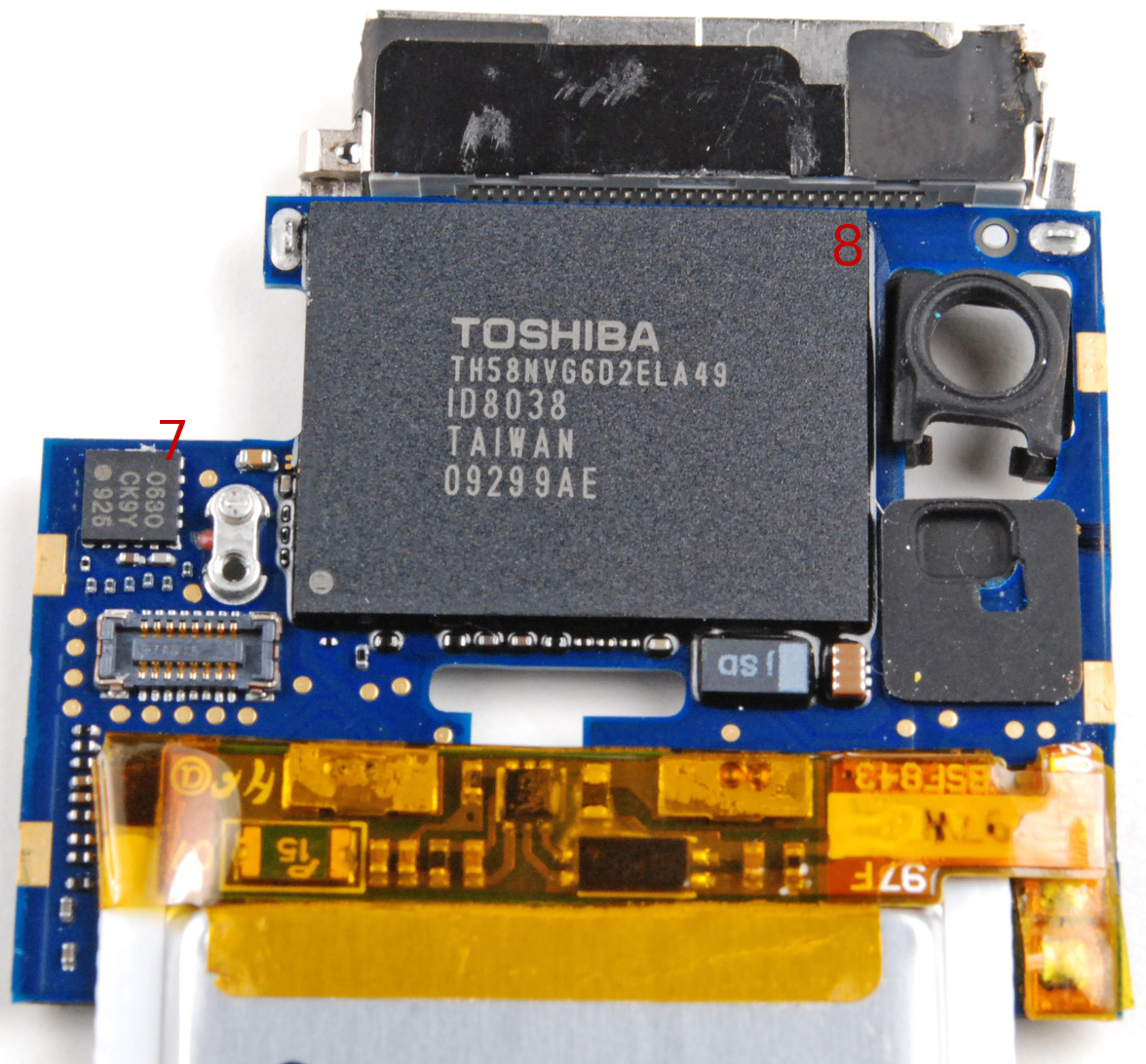

Components

| Label | Component | Part | Markings | Notes |

|---|---|---|---|---|

| 2 | CPU | Samsung S5L8730 | 339S0081 ARM, K4X51323PG-UGC6, EDE168AG 0928, APL0378A00, N1X2XW 0931 | Printed backwards on the chip - how sneaky. ARM1176JZF-S core (per CP15 data). |

| SDRAM | Integrated into the processor, similar to the iPod Touch and iPhone lines. | |||

| 8 | NAND Flash | Various 8/16 GB chips | TH58NVG6D2ELA49, ID8038, TAIWAN, 09299AE | One example is TH58NVG6D2ELA49 visible on the iFixit Teardown |

| 1 | Power manager | Probably Dialog | 338S0707, -AD, 09278HGZ | Similar looking and named chips like this have been power managers. Apple uses chips like these in just about every device. |

| 3 | ||||

| 4 | ||||

| 5 | Audio codec | Cirrus Logic CLI1480A | 338S0559, ATWV0926, SGP | Also found in the Touch 3G. Stereo CODEC w/ Headphone and Speaker Amp |

| 6 | Accelerometer | LIS331DLM | 33DM, 2910 | The newer Touch's, iPhone's, and even the iPad have similar accelerometers, and I've discovered a pattern in the chip names. |

| 7 | 0630, CK9Y, 925 |

CP15 Registers

Dump of CP15 registers from bootrom context:

| cX | cY | opc2 | Description | Value | Interpretation |

|---|---|---|---|---|---|

| 0 | 0 | 0 | Main ID | 410fb764 | ARM (0x41), Variant 0, Architecture: see CPUID, Part: ARM1176 |

| 0 | 0 | 1 | Cache Type | 1d152152 | Write back, format C cache lockdown, Register 7 cache cleaning operations, separate I/D caches; data cache: (no restriction on page allocation, 16KB, 4-way associative, 2 word line length) istrunction cache: (no restrictions on page allocation, 16KB, 4-way, 2 word) |

| 0 | 0 | 2 | TCM Status | 00000000 | No tightly coupled memory. |

| 0 | 0 | 3 | TLB Type | 00000800 | |

| 0 | 1 | 0 | Processor Feature 0 | 00000111 | Jazelle, Thumb1, ARM (no Thumb2) |

| 0 | 1 | 1 | Processor Feature 1 | 00000011 | Security Extensions Architecture v1, Standard ARMv4 programmer's model. No microcontroller model. |

| 0 | 1 | 2 | Debug Feature 0 | 00000033 | v6.1 Secure Debug, v6.1 Debug. |

| 0 | 1 | 3 | Auxiliary Feature 0 | 00000000 | |

| 0 | 1 | 4 | Memory Model Feature 0 | 01130003 | Standard ARM1176JZF-S. |

| 0 | 1 | 5 | Memory Model Feature 1 | 10030302 | Standard ARM1176JZF-S. |

| 0 | 1 | 6 | Memory Model Feature 2 | 01222100 | Standard ARM1176JZF-S. |

| 0 | 1 | 7 | Memory Model Feature 3 | 00000000 | Standard ARM1176JZF-S. |

| 0 | 2 | 0 | Instruction Set Feature Attribute 0 | 00140011 | Standard ARM1176JZF-S. |

| 0 | 2 | 1 | Instruction Set Feature Attribute 1 | 12002111 | Standard ARM1176JZF-S. |

| 0 | 2 | 2 | Instruction Set Feature Attribute 2 | 11231121 | Standard ARM1176JZF-S. |

| 0 | 2 | 3 | Instruction Set Feature Attribute 3 | 01102131 | Standard ARM1176JZF-S. |

| 0 | 2 | 4 | Instruction Set Feature Attribute 4 | 00001141 | Standard ARM1176JZF-S. |

| 0 | 2 | 5 | Instruction Set Feature Attribute 5 | 00000000 | Standard ARM1176JZF-S. |

| 1 | 0 | 0 | Control | 00450078 | No Force AP, no TEX remap, CPSR E set to 0 on exception, no VIC, no extended page tables, allow unaligned data access, no fast interrupts, global enable for instruction/data TCM, loads to PC set the T bit, random cache replacement, exceptions vectors at Vector Base Address Register. I$, D$ disabled by wInd3x, branch prediction disabled, no strict alignment fault checking, no MMU. |

| 1 | 0 | 1 | Auxiliary Control | 00000007 | ... |

| 1 | 0 | 2 | Coprocessor Access Control | 00000000 | ... |

| 1 | 1 | 0 | Secure Configuration | 00000000 | ... |

| 1 | 1 | 1 | Secure Debug Enable | 00000000 | ... |

| 1 | 1 | 2 | Non-Secure Access Control | 00000000 | ... |

| 2 | 0 | 0 | Translation Table Base 0 | 00000000 | ... |

| 2 | 0 | 1 | Translation Table Base 1 | 00000000 | ... |

| 2 | 0 | 2 | Translation Table Base Control | 00000000 | ... |

| 3 | 0 | 0 | Domain Access Control | 00000000 | ... |

| 7 | 4 | 0 | PCA | 00000000 | ... |

| 7 | 10 | 6 | Cache Dirty Status | 00000000 | ... |

| 9 | 0 | 0 | Data Cache Lockdown | fffffff0 | ... |

| 9 | 0 | 1 | Instruction Cache Lockdown | fffffff0 | ... |

| 9 | 1 | 0 | Data TCM Region | 00000000 | ... |

| 9 | 1 | 1 | Instruction TCM Region | 00000000 | ... |

| 9 | 1 | 2 | Data TCM Non-secure Control Access | 00000000 | ... |

| 9 | 1 | 3 | Instruction TCM Non-secure Control Access | 00000000 | ... |

| 9 | 2 | 0 | TCM Selection | 00000000 | ... |

| 9 | 8 | 0 | Cache Behavior Override | 00000000 | ... |

Helpful pages

Teardowns:

Other: